#### Recommended PCB Routing Guidelines for S34MLxx SLC NAND Flash Memory

**Author: Mohamed Sardi**

Associated Part Families: S34ML-1, S34ML-2

AN210081 provides general routing guidelines for PCBs designed with a SkyHigh S34MLxx SLC NAND memory device.

#### 1 Introduction

This application note provides general routing guidelines for PCBs (Printed Circuit Boards) designed with SkyHigh S34MLxx NAND Flash Memory Family. Following these guidelines does not eliminate the need to perform signalintegrity/power delivery and signal timing/crosstalk simulations, using the \$34ML-1 and \$34ML-2 SkyHigh-providedIBIS models. These guidelines only offer an initial reference towards a PCB design using a SkyHigh \$34MLxx memory device.

If the PCB design cannot meet or beat the recommendations in this application note, the PCB layout designer must run detailed simulations to ensure the exceptions do not degrade the desired performance.

This document applies to the following SkyHigh device families:

■ S34ML-1, S34ML-2

## 2 Signal Descriptions

Table 1 provides the S34MLxx SLC NAND flash memory device pin description.

Table 1. Pin Descriptions

| Pin Name           | Description                                                                                                                                                                                                                                 |  |  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| I/O0 - I/O7 (x8)   | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The I/O pins float to High-Z when the device is deselected or the outputs are disabled.                                                |  |  |

| I/O8 - I/O15 (x16) |                                                                                                                                                                                                                                             |  |  |

| CLE                | Command Latch Enable. This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                             |  |  |

| ALE                | Address Latch Enable. This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                             |  |  |

| CE#                | Chip Enable. This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                       |  |  |

| WE#                | Write Enable. This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                           |  |  |

| RE#                | Read Enable. The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |  |  |

| WP#                | Write Protect. The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                   |  |  |

| R/B#               | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                |  |  |

| VCC                | Supply Voltage. The $V_{CC}$ supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$ .                                           |  |  |

| VSS                | Ground.                                                                                                                                                                                                                                     |  |  |

| NC                 | Not Connected.                                                                                                                                                                                                                              |  |  |

Table 2 groups the S34MLxx SLC NAND flash memory signals in the order of ascending signal integrity priority constraints.

Table 2. Signals Grouping with Signal Integrity (SI) Constraints Priority

| Signal Type        | Pin Name      | Priority                  |

|--------------------|---------------|---------------------------|

| Data               | IO15-IO0      | SI Constraints Priority 1 |

| Read/Write Control | RE#, WE#      | SI Constraints Priority 2 |

| Other Control      | ALE, CLE, CE# | SI Constraints Priority 3 |

| Other signals      | WP#, RY/BY#   | SI Constraints Priority 4 |

| Power/Ground       | VCC, VSS      | Refer to section 5        |

The SI constraints priority does not necessarily mean the routing priority order but the importance of treating that particular group of signals as a high-speed signal. A common best practice is to route the Control signals first and then use timing relationship between signals provided in the datasheet to determine the actual trace lengths of the other signals.

#### 3 Package Breakout Routing Recommendations

SkyHigh recommends that all signals be broken out on the top layer of the PCB stackup. The power balls/pins (VCC) and ground balls/pins (VSS) can be connected to the nearest power/ground plane through power/ground vias. These vias must be located as close as possible to the S34MLxx power and ground ball/pins.

The S34MLxx comes in three packages:

- 63-ball grid FBGA

- 67-ball grid BGA

- 48-pin TSOP

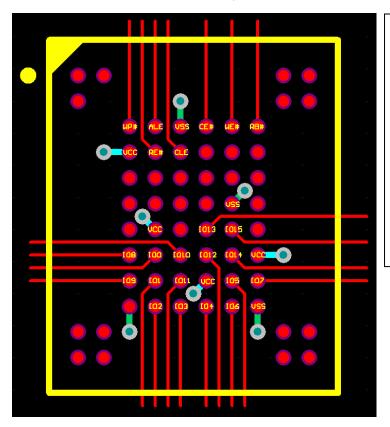

The Figure 1, Figure 2, and Figure 3 provide respective PCB breakout recommendations for the 63 FBGA, 48 FBGA, and 48TSOP packages.

Figure 1 FBGA 63 PCB breakout (Top View, Balls Down)

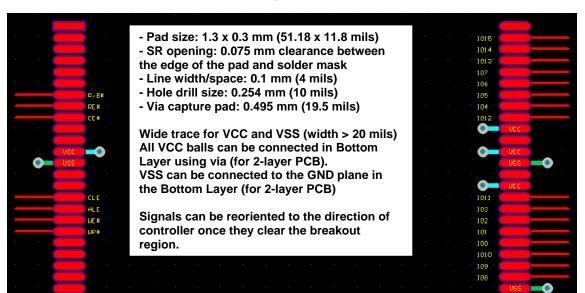

- Pad size: 0.35 mm (13.78 mils)

- SR (Solder Resist) opening: 0.5 mm (19.69 mils)

- Line width/space: 0.1 mm (4 mils)

- Hole drill size: 0.254 mm (10 mils)

- Via capture pad: 0.495 mm (19.5 mils)

Wide trace for VCC and VSS (width > 20 mils)

All VCC balls can be connected in Bottom Layer

using via (for 2-layer PCB).

VSS can be connected to the GND plane in the

Bottom Layer (for 2-layer PCB)

Signals can be reoriented to the direction of controller once they clear the breakout region.

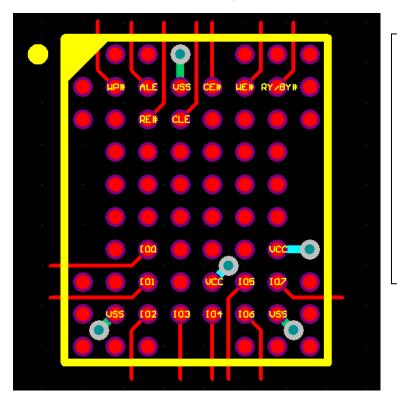

Figure 2 FBGA 67 PCB breakout (Top view, balls down)

- Pad size: 0.35 mm (13.78 mils)

- SR opening: 0.5 mm (19.69 mils)

- Line width/space: 0.1 mm (4 mils)

- Hole drill size: 0.254 mm (10 mils)

- Via capture pad: 0.495 mm (19.5 mils)

Wide trace for VCC and VSS (width > 20 mils)

All VCC balls can be connected in Bottom

Layer using via (for 2-layer PCB).

VSS can be connected to the GND plane in

the Bottom Layer (for 2-layer PCB)

Signals can be reoriented to the direction of controller once they clear the breakout region.

Figure 3 TSOP Land pattern (x8, x16)

## 4 General PCB Signal Routing Guidelines

For simplicity, the recommendations in this application note assume a point-to-point routing topology between a memory flash controller and a SkyHigh S34MLxx NAND flash. Star or T topologies are not considered in this document. If one of these topologies is used, the PCB design engineer must ensure that appropriate terminationresistors are determined based on IBIS simulations. Using NAND flash in a daisy-chain topology is not recommended.

The following general guidelines must be considered before and throughout the PCB layout design effort:

- Calculate the impedance of the trace by determining the exact values of signal trace length, width, and trace spacing.

- Use the VSS plane as a primary reference or return path for all signals. Power should only be considered as secondary reference option where a solid continuous ground reference is also present.

- Avoid multiple vias on reference planes to eliminate or minimize return current discontinuity.

- Try to avoid routing signal traces at the edge of the reference plane.

- Route the identified longest signal trace first before routing and adjusting the length of other signal traces.

- Route the same signal groups on the same signal layer and follow the routing from pin to pin as a group (that is, route them together).

- Isolate the ground return path of analog signals from digital signals; i.e. separate digital and analog grounds.

- Use signal integrity tools to estimate actual trace velocity and path delays to ensure that the assumptions

mentioned are not violated.

- Perform signal integrity simulations using SkyHigh-provided IBIS models.

## 5 Stackup Recommendations

Irrespective of PCB stackups chosen, reference all the signal traces to a solid ground plane and dedicate a power plane. The most straightforward stackup to meet this recommendation is a minimum of a 4-layer stackup with the following composition:

- Top Layer (Signal): Add as many GND guard traces next to NAND signals as possible and connect to GND plane using vias.

- GND

- VCC

- Bottom layer (Signal): Add as many GND guard traces next to NAND signals as possible and connect to GND plane using vias.

It is possible to route S34MLxx NAND flash in a 2-layer PCB as long as all signals are properly GND referenced and VCC trace widths are kept as wide (>20 mils) as possible.

## 6 Signal Routing Length, Spacing, and Geometry Constraints

The PCB electrical properties and the recommendations (length, spacing, and geometry constraints) in this application note are based on dielectric material with FR4 assumption. When adjusting signals trace length, a rule of thumb to remember is that routing 1 inch adds a delay of approximately 166 ps. The signal routing lengths are considered from package pin (source) to package pin (destination) by considering the package length compensation while the signal routing spacing between two traces is considered from center to center.

Do the following to achieve a PCB layout with optimal signal integrity and timing margins:

- 1. Refer to controller and S34MLxx datasheet timing diagrams to generate AC timing equations for key parameters such as t<sub>DS</sub>, t<sub>DH</sub>, t<sub>CH</sub>, t<sub>CLH</sub>, t<sub>REA</sub>, and t<sub>ALS</sub>.

- 2. **Keep the signal trace impedance around 50 ohms+/-10%.** The Data trace impedance depends on the stackup but also the trace width and the traces spacing. Based on a 4-layer PCB stackup, this 50-Ω impedance requirement corresponds to a trace width of about ~4 to 6 mils and a spacing between traces of about ~3x the trace width (~12 to 18 mils).

- 3. Determine the signal capacity loading. The absolute maximum total length of signals with respect to their reference plane is defined by the total load capacitance, which directly affects the signal quality.

- a. Keep the total load capacitance less than the C<sub>LOAD</sub> value provided in the datasheet. Allow a margin for spurious/parasitic capacitances that cannot be modeled well.

- b. Total load capacitance includes:

- i. Total line length capacitance (~3.3 pF/inch with FR4 assumption),

- ii. Max pin capacitance of controller,

- iii. Capacitance of any intermediary devices such as connectors and series resistors as well as the parasitic capacitance of connected devices.

- 4. Route the two WE# and RE# Control signals first and determine the length mismatch requirements for Data bus, ALE, and CLE signals based on the datasheet timing relationship (skew) requirement:

- a. WE# length determines the length mismatch requirements with I/O through t<sub>DS</sub>/t<sub>DH</sub>, ALE through t<sub>ALS</sub>/t<sub>ALH</sub>, CE through t<sub>CLHR</sub>, and CLE through t<sub>CLHR</sub>.

- b. RE# length depends upon the controller access time equation that includes t<sub>REA</sub>, t<sub>REH</sub>, and t<sub>RC</sub>.

SkyHigh recommends the following length mismatch guidelines:

| Signal Group           | Length Match Tolerance        |

|------------------------|-------------------------------|

| Data                   | +/- 500 mils within the group |

| WE# to Data            | +/- 500 mils                  |

| CLE, CLE, ALE to WE    | +/- 500 mils                  |

| CE to RE# & CLE to RE# | +/- 500 mils                  |

Document Number: 002-10081 Rev. \*B

During the length mismatch analysis, the PCB designer must pay attention to signal polarities (rising and falling edge triggers) as well as lead/lag timing to determine whether a specific Control signal should always lead or lag compared to another signal or data bus.

- 5. Route WP# and R/B trace to be as short as possible and consider t<sub>RR</sub> and WP timing.

- 6. Consider the following trace spacing (center-to-center) guidelines to minimize crosstalk effects that can affect signals integrity and delays:

- c. Trace spacing within a signal group should be > 3x dielectric height (H) between the signal and ground reference.

- d. Trace spacing between signal groups should be > 3x trace width.

- e. Trace spacing between NAND signals and other interface signals should be > 3X trace width.

#### 7 Termination

A PCB layout designer must perform the following steps to ensure a proper termination on NAND flash signal traces:

- 1. Review the drive strength and impedance required for the NAND controller I/O and the transmission line routing load to determine whether series terminations are needed. The drive strength can easily be determined by looking at the IBIS IV/VT curves for the three PVT corners (typical, min, and max).

- 2. Add pull-up resistor on the R/B# signal trace (see the datasheet for the exact value).

### 8 Power Delivery Guidelines

Do the following to ensure a proper routing power delivery on NAND flash VCC and VSS signal traces:

- 1. Connect VSS balls/pins to the ground plane. Connect each VSS ball/pin to the internal GND plane with its own unique via to minimize IR drop.

- Connect VCC balls/pins to a single supply plane. Connect each VCC ball/pin to the internal supply plane with its

own unique via as to minimize IR drop. If a 2-layer PCB is used, all VCC vias must be connected together as

close to the NAND package with thick traces.

- 3. Where possible, keep at least 20-mil gap between power planes.

- 4. If possible, provide at least an 80-mil gap between power islands on the same layer.

- 5. VCC islands must be large enough and not have "bottle necks." The power island must be at least 250-mils wide at the narrowest area.

- 6. Except in the package breakout area, maintain a minimum trace width of 20 mils for all supply traces. Both supply and ground traces (or planes) must be closely coupled to each other (i.e., route them close to each other to avoid large inductive loops).

- 7. Keep supply trace lengths  $\leq$  400 mils and tracing width  $\geq$  20 mils.

- 8. Maintain low-impedance routing (traces >20 mils) from voltage regulator to flash supply pins as well as from voltage regulator to the controller flash supply pins.

- 9. If the voltage regulator is not on the same PCB as the flash packages (modularization), aim to the reach the lowest impedance on VCC/VSS routing (e.g., wider traces).

- 10. If the controller main board and memory module are not on the same board, it is recommended to use a *G: S/P: G* type of connector configuration where S refers to signal, G refers to GND, and P refers to VCC.

- 11. Add VCC/GND test points as close to each flash package as well as next to voltage regulator module (VRM). This allows measurement of the VCC-GND waveform at both VRM as well as flash packages.

- 12. Add decoupling capacitors using the following recommendations:

- a. Place PCB decoupling capacitors as close to the package as possible.

- b. Place at least two 1-µF 0402 ceramic capacitors near each side of the package.

- c. Ensure that these capacitors have low ESL (Equivalent Series Inductance) and ESR (Equivalent Series Resistance).

- Keep the VCC and GND trace routing from the capacitor as wide as possible to avoid inductive/resistive

effects.

Document Number: 002-10081 Rev. \*B

e. In addition to the decoupling capacitors, place two 0.1- $\mu F$  0402 ceramic capacitors as close to the package as possible.

f. Use X7R or X5R ceramic capacitors with the rated voltage greater than or equal to twice VCC max.

#### 9 Test Points and Oscilloscope Measurements

Test points are often added on the PCB to make some measurements or probing some signals. The following list provides recommendations on where and how to place these test points:

- 1. For IO0-15 and R/B# signals, add test points as close to controller and S34MLxx NAND flash. For other signals, add test points close to the S34MLxx NAND flash memory package.

- 2. When the memory controller is driving, probe the signals as close as possible to the NAND flash. When the NAND flash is driving, probe the signals as close as possible to the memory controller.

- 3. While creating the test pad, the stub (extra inductance and capacitance) resulting from such pads should be minimized. Probing at the break-out via is better than creating test pad stubs. In the case of 4-layer PCB with through-hole vias, if possible, probe the signals at the bottom of the PCB on these vias.

- 4. While performing scope measurements, use a 3-GHz or greater bandwidth scope and low-impedance probes to see the waveform transition (such as rising and falling portion of the waveform) more accurately.

- 5. Always measure VCC-VSS at the controller, voltage regulator, or next to the connector (either side) and at flash. This needs to be done before making any signal measurements to ensure that the supply is not noisy. A noisy supply impacts signal timing. In addition, these measurements establish the IR drop from regulator to controller OR regulator to flash.

- 6. While measuring signals, it is a good idea to set the trigger on the most common switching signals such as WE#.

#### 10 Conclusion

This application note provides general routing guidelines for PCBs designed with a S34MLxx flash memory device. For any questions regarding this application note, contact your SkyHigh representative.

# **Document History**

Document Title: AN210081 - Recommended PCB Routing Guidelines for S34MLxx SLC NAND Flash Memory

Document Number: 002-10081

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change       |

|----------|---------|--------------------|--------------------|-----------------------------|

| **       | 5054667 | МОН                | 12/17/2015         | New Spec.                   |

| *A       | 5789204 | AESATP12           | 07/04/2017         | Updated logo and copyright. |

| *B       |         | MNAD               | 05/24/2019         | Updated to Skyhigh format.  |